半導体テクノロジーに関連する気になるカタログにチェックを入れると、まとめてダウンロードいただけます。

設計エラーの早期検出とは?課題と対策・製品を解説

目的・課題で絞り込む

カテゴリで絞り込む

検査・測定装置 |

材料 |

自動化・ITソリューション |

製造装置 |

関連技術 |

その他半導体テクノロジー |

回路・パターン設計における設計エラーの早期検出とは?

各社の製品

絞り込み条件:

▼チェックした製品のカタログをダウンロード

一度にダウンロードできるカタログは20件までです。

電気設計専用CADソフト「ECADシリーズ」では、予想がつかない

アクシデントに対して、ビジネスへのインパクトを最小限に抑えるための

サポートサービス『サポート契約』をご用意しています。

当サービスにご加入いただくと、機能追加や安定性が向上するバージョンアップ版の無償提供、ECADユーザー限定『ECADカスタマーサポートサイト』、特別価格または無償でのトレーニング、故障プロテクタやインストールメディアの無償交換などの充実したサポートサービスをご利用いただけます。

お客様が最高の環境で、最高の結果を得ていただくために、サポート契約へのご加入をお勧めします。

『SView・SView-PC』は、大規模GDS2ストリームデータを高速に

表示して手軽に確認ができるレイアウトビューアです。

DRCで発生した擬似エラーの内容確認が容易にでき、実エラーか

否かを判断できます。

また、使用頻度の高いレイアウト設計CADプログラムを使用せずに、

レイアウトデータの内容確認作業が単独でしかも容易にできるため、

設計CADプログラムの使用効率が高まります。

【特長】

■既存のレイアウトデータの内容確認がすぐできる

■必要なデータの発見が容易

■GDS2ストリームデータの気になるポイントも直ちに確認が可能

■DRCで発生した擬似エラーの内容確認が容易にできる

■設計CADプログラムの使用効率が高まる

※詳しくはPDF資料をご覧いただくか、お気軽にお問い合わせ下さい。

個(人)を尊重し、互いに信頼しあえる企業風土を築き、その能力を最大限に結集することにより、価値のある技術・製品を生み出し、社会・文化への貢献を期す。

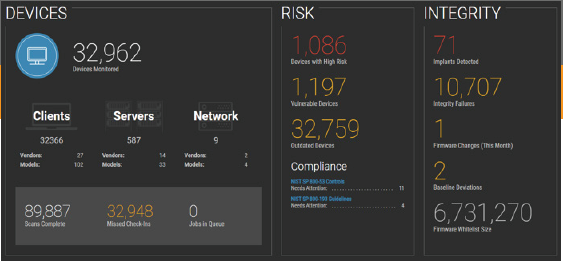

当社の、ファームウェアの脆弱性や改ざんの兆候を可視化する

『VBOS対策ソリューション』をご紹介します。

ファームウェアの改ざんや変更の有無(Integrity)を

検知することが可能。

また、対処すべき脆弱性が存在する場合、脆弱性の詳細の確認や、

パッチを適用できます。

【特長】

<可視化>

■ファームウェアに存在する脆弱性(Risk)を可視化

■1つのダッシュボードで一元的に管理することが可能

■ファームウェアに存在する脆弱性についても可視化

■脆弱性の概要、攻撃事例、修復方法を提示することが可能

※詳しくはPDF資料をご覧いただくか、お気軽にお問い合わせ下さい。

DiXiM Security Endpoint は、POSレジや複合機などストレージをもつ産業機器への組み込みを想定したアンチウイルスセキュリティサービスです。LinuxおよびWindows OS上で動作し、ストレージ内のファイルへの読み書きを監視しながら、最新の脅威情報を元に悪意のあるファイルを検出、隔離、駆除、削除します。

【特長】

■EUトップベンダーESET社の脅威情報を利用

第三者セキュリティテスト機関から100回以上受賞獲得しているEUトップベンダーであるESET社より提供を受けた最新の脅威情報をもとに、脅威検索を行います。

『非接触ホバーセンサ』は、

既存システムに載せてUSBケーブルを挿すだけで

簡単にタッチフリー(空中タッチ)を実現する透明ガラスセンサです。

不特定多数の人が触れる場所や、医療施設・食品工場など衛生管理の厳しい状況で、

直接触れずに操作することで不安をなくし、安心・安全で清潔な環境を提供します。

感染対策や汚れ防止、清掃頻度の削減にも繋がります。

【特長】

■センサ表面から約5cm離れた位置での指検出を実現

■手袋を装着した状態での操作も可能

■独自開発のアルゴリズムでタッチパネル同様の直感的な操作

■用途・使用環境に合わせた検出高さの変更が可能

■専用ドライバインストール不要でUSBケーブルを挿すだけの簡単接続

※詳しくはPDF資料をご覧いただくか、お気軽にお問い合わせ下さい。

『IntelliSuite』は、半導体素子の製造工程を利用したマイクロマシン(MEMS)の

製造工程の検討から、デバイスの性能評価まで一貫して検討することを

目的とした、統合型の設計・解析ソフトウェアです。

汎用性を持たせることによる弊害の排除、数値解析におけるユーザー負担の

軽減を実現し、効率的な解析結果の取得を促すことで、MEMS開発における

負担の軽減を実現しています。

【特長】

■専門技術間のシームレスなデータ連携を実現するソフトウェア設計環境

■等価回路要素による高速設計機能

■MEMS構造設計者向けデザインルールチェック

■Optical,Piezo,Sensor,RF,Bio,他の各種MEMSに対応

■ASIC設計との連携機能

※詳しくはPDF資料をご覧いただくか、お気軽にお問い合わせください。

当社は、エレクトロニクス会社として幅広い分野の

設計・検証・評価を手掛けていきます。

受託・請負設計スタイルを主とし、派遣型から請負型へ、

請負型から受託型へビジネスパートナーとして技術

ソリューションをご提供。

常に革新、創造を意識し、パートナーとしての新しい

取り組みにも参画していきます。

【事業内容】

■LSI設計/検証・第三者検証サービス

■FPGA・PCB設計/検証サービス

■SOFT設計/検証(ITシステム)サービス

※詳しくはPDF資料をご覧いただくか、お気軽にお問い合わせ下さい。

当社のでは、長年にわたるASIC/FPGA設計の豊富な経験を活かし、

お客様の用途に合わせて、ご提案・開発支援を行う『LSI設計サービス』を

提供しております。

仕様検討、設計書作成、RTLコーディング、論理検証からカバレッジ検証等

幅広く対応可能です。

ご要望の際はお気軽に、お問い合わせください。

【サービス内容】

■ASIC開発

■FPGA開発

■評価解析

※詳しくは、お気軽にお問い合わせください。

個(人)を尊重し、互いに信頼しあえる企業風土を築き、その能力を最大限に結集することにより、価値のある技術・製品を生み出し、社会・文化への貢献を期す。

当社では、Atilia Technology社製『CMOS 32Gb/s パルスパターンジェネレータ』を

取り扱っております。

本パルスパターン発生器(PPG)「P1」は、CMOSベース32Gb/s、またそれ以上の

ビットレートまで高い品質の作動出力データを提供します。

外部ハーフレート方式(すなわち32Gb/sデータの場合、16GHzのクロックインプット)

によって駆動し、27-1、215-1、223-1、231-1の疑似ランダムパターン(PRBS)を

出力できると共に10-3、10-6、10-9及び0のエラーを挿入できます。

【特長】

■高性能

■コンパクトで低価格

■独立したパルスパターン設定

■最大60psのスキュー設定が可能

■2ch、4chタイプもご用意

※英語版カタログをダウンロードいただけます。

※詳しくはPDF資料をご覧いただくか、お気軽にお問い合わせ下さい。

『Quadcept Force』の"CCM(Cloud Component Manager)"では、

部品ライブラリを一元管理することで、従来の運用課題を解決に導きます。

CCMと電子部品DBを連携させることにより、部品EOL予測情報・環境データ・

データシートを取得し、EOL発生時に設計図面上で代替部品の比較や選定が可能。

社内の基幹システムやPDM、ERPと柔軟に同期でき、既存システムも

生かすことで高いパフォーマンスを発揮します。

【特長】

■CCMと電子部品DBを連携させることで、部品EOL予測情報・

環境データ・データシートを取得

■今あるシステムとの柔軟な連携が可能

■純国産の製品で大規模な組織でも安心

■データの一元管理により曖昧管理から脱却

※詳しくは関連リンクをご覧いただくか、お気軽にお問い合わせ下さい。

お探しの製品は見つかりませんでした。

1 / 1

回路・パターン設計における設計エラーの早期検出

回路・パターン設計における設計エラーの早期検出とは?

半導体製造プロセスにおいて、回路設計およびパターン設計段階で発生するエラーを、開発の初期段階で発見・修正すること。これにより、手戻りによる開発期間の遅延やコスト増大を防ぎ、製品の品質向上と市場投入までの時間短縮を目指す。

課題

複雑化する設計と検証工数増大

半導体デバイスの機能高度化・集積度向上に伴い、回路・パターン設計は極めて複雑化し、手作業や従来の検証手法ではエラーの見落としリスクが高まっている。

設計サイクルの長期化とコスト増

設計エラーが後工程で発見されると、大幅な手戻りが発生し、開発期間の長期化とそれに伴う莫大なコスト増を招く。

検証漏れによる品質低下リスク

限られたリソースの中で全ての設計要素を網羅的に検証することは困難であり、見落とされたエラーが製品の信頼性や性能に悪影響を与える可能性がある。

設計者間の知識・経験のばらつき

設計者のスキルや経験に依存したエラー検出では、一定の品質を保つことが難しく、属人的なリスクを抱えることになる。

対策

自動化された静的検証ツールの活用

設計ルールチェック(DRC)やレイアウト対回路図比較(LVS)などの自動化ツールを導入し、設計初期段階でルール違反や不整合を網羅的に検出する。

シミュレーション・モデリングによる早期検証

回路シミュレーションや物理現象のモデリングを活用し、設計段階で電気的特性や物理的な問題を予測・評価することで、潜在的なエラーを早期に発見する。

設計フローへの継続的インテグレーション(CI)導入

設計変更の度に自動検証を実行するCIプロセスを導入し、エラーの早期発見と迅速な修正サイクルを実現する。

AI・機械学習を活用した異常検知

過去の設計データやエラーパターンを学習させたAI・機械学習モデルを用いて、人間が見落としがちな微妙なエラーや異常なパターンを自動的に検知する。

対策に役立つ製品例

設計ルールチェックソフトウェア

設計データが製造プロセスにおける物理的な制約やルールに準拠しているかを自動的に検証し、レイアウト上の問題を早期に検出する。

回路シミュレーションシステム

設計された回路の電気的特性を詳細にシミュレーションし、意図しない動作や性能低下を引き起こす可能性のあるエラーを特定する。

レイアウト検証自動化システム

回路図とレイアウトの整合性を自動的に比較検証し、配線ミスや接続漏れなどの設計エラーを効率的に発見する。

AI駆動型設計解析ツール

過去の設計データから学習したパターン認識能力により、複雑な回路やレイアウトにおける潜在的なエラーや異常を予測・検知する。

⭐今週のピックアップ

読み込み中