半導体テクノロジーに関連する気になるカタログにチェックを入れると、まとめてダウンロードいただけます。

設計データの検証時間短縮とは?課題と対策・製品を解説

目的・課題で絞り込む

カテゴリで絞り込む

検査・測定装置 |

材料 |

自動化・ITソリューション |

製造装置 |

関連技術 |

その他半導体テクノロジー |

回路・パターン設計における設計データの検証時間短縮とは?

各社の製品

絞り込み条件:

▼チェックした製品のカタログをダウンロード

一度にダウンロードできるカタログは20件までです。

電気設計専用CADソフト「ECADシリーズ」では、予想がつかない

アクシデントに対して、ビジネスへのインパクトを最小限に抑えるための

サポートサービス『サポート契約』をご用意しています。

当サービスにご加入いただくと、機能追加や安定性が向上するバージョンアップ版の無償提供、ECADユーザー限定『ECADカスタマーサポートサイト』、特別価格または無償でのトレーニング、故障プロテクタやインストールメディアの無償交換などの充実したサポートサービスをご利用いただけます。

お客様が最高の環境で、最高の結果を得ていただくために、サポート契約へのご加入をお勧めします。

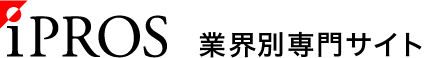

CDC研究所は、エンジニア向け「All in One」クラウドシステムを

提供しております。

当社では随時、"賛助会員"、"EDA利用会員"を募集しています。

お気軽にお問い合わせ下さい。

【タイプ別 用途例】

■デザインレビュー、ツール開発、FTPサーバ代替、データバックアップ

■設計・開発(ツール時間単価、期間利用)

■設計・開発(ツール時間単価、期間利用)+ツール優先利用

■設計・開発(ツール時間単価、期間利用)+ツール占有利用

■CDC研究所の環境上に、特定ユーザのLSI設計環境構築サポート

■All in One(利用会員の技術を含め、インプリに向けた請負サポート)

※詳しくはPDF資料をご覧いただくか、お気軽にお問い合わせ下さい。

当社では、Atilia Technology社製『CMOS 32Gb/s パルスパターンジェネレータ』を

取り扱っております。

本パルスパターン発生器(PPG)「P1」は、CMOSベース32Gb/s、またそれ以上の

ビットレートまで高い品質の作動出力データを提供します。

外部ハーフレート方式(すなわち32Gb/sデータの場合、16GHzのクロックインプット)

によって駆動し、27-1、215-1、223-1、231-1の疑似ランダムパターン(PRBS)を

出力できると共に10-3、10-6、10-9及び0のエラーを挿入できます。

【特長】

■高性能

■コンパクトで低価格

■独立したパルスパターン設定

■最大60psのスキュー設定が可能

■2ch、4chタイプもご用意

※英語版カタログをダウンロードいただけます。

※詳しくはPDF資料をご覧いただくか、お気軽にお問い合わせ下さい。

『SView・SView-PC』は、大規模GDS2ストリームデータを高速に

表示して手軽に確認ができるレイアウトビューアです。

DRCで発生した擬似エラーの内容確認が容易にでき、実エラーか

否かを判断できます。

また、使用頻度の高いレイアウト設計CADプログラムを使用せずに、

レイアウトデータの内容確認作業が単独でしかも容易にできるため、

設計CADプログラムの使用効率が高まります。

【特長】

■既存のレイアウトデータの内容確認がすぐできる

■必要なデータの発見が容易

■GDS2ストリームデータの気になるポイントも直ちに確認が可能

■DRCで発生した擬似エラーの内容確認が容易にできる

■設計CADプログラムの使用効率が高まる

※詳しくはPDF資料をご覧いただくか、お気軽にお問い合わせ下さい。

シリアルATA(SATA)IPコアは、Serial ATA Revision 3.0に準拠しており、, Xilinx製UltraScale, 7シリーズ, Intel 10シリーズ等のFPGAデバイスでで動作するデザインとなっています。 本IPコアはリンク層のみの提供ですが、リファレンスデザインとしてトランスポート層および物理層デザインが用意されており、PHYチップなしでSATA3ハードディスクとの接続が可能です。

本SATA-IPコアは、SSDのパフォーマンスを最大限に引き出し、1ch当たり500MB/s超の高速転送が実現可能です。各種FPGAボード用時間限定版評価デモファイルを準備しており、購入前にパフォーマンスを実機で評価することができます。

またコア製品にはXilinx/Intel各種 FPGA評価ボード上で動作するリファレンス・デザインが標準添付されており、このリファレンス・デザインをベースとして開発をスタートできるため、短期間での製品開発が可能です。

『Quadcept Force』の"CCM(Cloud Component Manager)"では、

部品ライブラリを一元管理することで、従来の運用課題を解決に導きます。

CCMと電子部品DBを連携させることにより、部品EOL予測情報・環境データ・

データシートを取得し、EOL発生時に設計図面上で代替部品の比較や選定が可能。

社内の基幹システムやPDM、ERPと柔軟に同期でき、既存システムも

生かすことで高いパフォーマンスを発揮します。

【特長】

■CCMと電子部品DBを連携させることで、部品EOL予測情報・

環境データ・データシートを取得

■今あるシステムとの柔軟な連携が可能

■純国産の製品で大規模な組織でも安心

■データの一元管理により曖昧管理から脱却

※詳しくは関連リンクをご覧いただくか、お気軽にお問い合わせ下さい。

SDIOWorxは、SD規格2.0に従って、SDIO Hostコントローラとクライアントカード/デバイスに対応するドライバサポートを完備しています。Embedded SDIOWorxフレームワークに含まれているソフトウェアはSD/MMC/SDHC/eMMC Storage、及び組み込みデバイス内のSDIOコントローラ/周辺機器をサポートできます。

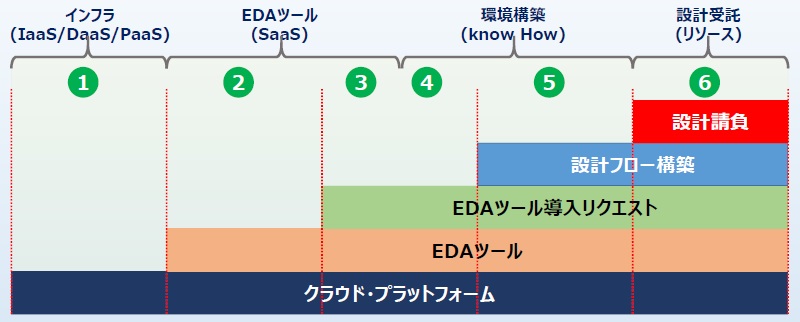

『UAP6200N』は、高速データ処理用にFPGAを2個搭載している

8Bit、6Gsps 2channel + FPGA ボードです。

データ出力FPGA(Virtex-4)から、6Gbps(実効速度)の高速シリアル出力

4チャネル装備していますので、最大24Gbps までのデータ出力が可能。

また、FPGA での入出力(特に、超高速アナログ入信号処理)につきましては

標準のIP ライブラリィが用意されています。これにより、ユーザは

信号処理部分の実装に専念する事ができます。

【特長】

■広帯域アナログデータサンプリング 6Gsps 8Bits 2Ch

■高速データ処理用にFPGA 2個搭載

・Virtex5:高速信号処理

・Virtex4:データ出力用

■高速シリアル出力をサポート

・3Gbps(Max.):4出力、4入力

・6Gbps(Max.):4出力

※詳しくはPDF資料をご覧いただくか、お気軽にお問い合わせください。

『IntelliSuite』は、半導体素子の製造工程を利用したマイクロマシン(MEMS)の

製造工程の検討から、デバイスの性能評価まで一貫して検討することを

目的とした、統合型の設計・解析ソフトウェアです。

汎用性を持たせることによる弊害の排除、数値解析におけるユーザー負担の

軽減を実現し、効率的な解析結果の取得を促すことで、MEMS開発における

負担の軽減を実現しています。

【特長】

■専門技術間のシームレスなデータ連携を実現するソフトウェア設計環境

■等価回路要素による高速設計機能

■MEMS構造設計者向けデザインルールチェック

■Optical,Piezo,Sensor,RF,Bio,他の各種MEMSに対応

■ASIC設計との連携機能

※詳しくはPDF資料をご覧いただくか、お気軽にお問い合わせください。

1、特徴と応用

・多入力多出力の光ハブ装置において、その光挿入損失補償するために半導体増幅器SOAを

内蔵した増幅機能付き光ハブ装置SOA-HUBです。

・光の伝送路には、光スプリッタや光カプラ—が良く利用されますが、

その接続ごとに光損失を生じます。とくに、光ハブは、入力側の光カプラおよび

出力側の光スプリッターで損失があり、このような損失補償にSOAが便利に利用できます。

2機能

・長波長帯のCWDM光源からの1.5μm帯の光を10dB以上増幅する機能を有するSOAを光ハブ装置に

内装することにより、損失の補償された構成の小型の光ハブ装置ができます。

・SOAの特性の詳細は、SOAのカタログをご参照ください。

※詳細は資料請求まで

当社のでは、長年にわたるASIC/FPGA設計の豊富な経験を活かし、

お客様の用途に合わせて、ご提案・開発支援を行う『LSI設計サービス』を

提供しております。

仕様検討、設計書作成、RTLコーディング、論理検証からカバレッジ検証等

幅広く対応可能です。

ご要望の際はお気軽に、お問い合わせください。

【サービス内容】

■ASIC開発

■FPGA開発

■評価解析

※詳しくは、お気軽にお問い合わせください。

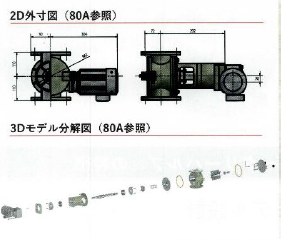

新工場を建設中の半導体メーカー様へ『ロータリーバルブ』を製作した

事例をご紹介いたします。

同社では、特殊仕様のロータリーバルブが必要で、工期の関係上3か月で

入手しなくてはなりませんでした。

当社は、設計から製作や検証、溶接加工から機械加工まで、全て一貫して

自社工場で行う為、全体として非常に圧縮された納期を実現。

ご希望の日程までに納品することができました。

【課題点】

■特殊仕様のロータリーバルブが必要

■従来取引のあるメーカーに相談したが、納期が6か月かかるとの回答を受けた

■新工場の工期の関係上、3か月で入手しなくてはいけない

■他のメーカーに相談したところで、1から説明していてはとても間に合わない

※詳しくはPDF資料をご覧いただくか、お気軽にお問い合わせ下さい。

当社では、LSI設計環境構築サービスを行っております。

LSI設計環境の検証および構築作業、LSI設計ツールの検証および

立ち上げ作業、LSI/VC設計ガイドラインの作成/編集など

LSI設計インフラについて幅広くサービスを展開。

また、LSI設計知識およびLSI設計インフラ知識(ライブラリ、プロセス、

上流設計ツール、下流設計ツール)を持ち合わせておりますので、

短期間でサービスが完了できます。

【このようなご要望にお応え】

■新規購入を検討している設計ツールの評価

■設計ツール購入後の立ち上げ

■異なるEDAベンダー社製品で構築されている設計環境の最適化

■End User様からのご要望にリソースが避けない

■コンサルティング・サービスで他社のツールが操作できない

※詳しくはPDFをダウンロードしていただくか、お気軽にお問い合わせください。

熱管理を成功させる鍵となるのは、稼働時間と信頼性です。そのため、長期信頼性が確保できるよう設計された、高品質な製品が必要です。ウルトラフローは、フラットフェースデザインで液だれがなく耐久性に優れた、液冷式高性能エレクトロニクスのためのクイック・カップリングです。高い流量特性、低圧力損失で冷却装置の寿命改善、ランニングコストの低減を実現します。

株式会社CDC研究所では、仮想マシンを自由に増減させながらシームレス

な開発を気軽に実現する『LSI開発クラウドプラットフォーム』を

提供しています。

環境をシェアするシステムなので、各種サーバーのメンテナンスも不要。

スキルの高いアドミニストレーターがいなくともプロジェクト管理が

容易に可能です。

【特長】

■堅牢なセキュリティ化でテレワークを実現

■EDAツール/VMをタイムシェア

■プロジェクトごとの設計スタイルを自由に設定

■暗号化通信を採用し、安全対策万全

■三大ベンダー対応

※詳しくはPDF資料をご覧いただくか、お気軽にお問い合わせ下さい。

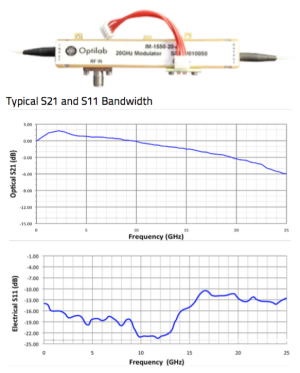

『IM-1550-20-a/P』は、TDMとWDM用20Gb/s伝達のために設計された

Optilab社製20GHz LN光強度変調器です。

-30~+60℃において優れた温度特性を有し、低挿入損失で長距離伝送を

可能にしております。

人工衛星リンク、アンテナリモーティング、ROF用として最大20GHzまでの

アナログ光変調器としてお使い頂けます。

【特長】

■TDMとWDM用20Gb/s伝達のために設計

■-30~+60℃において優れた温度特性

■低挿入損失で長距離伝送が可能

■バイアスポートはSMAコネクタタイプ、基板タイプから選択可能

■オートバイアス回路・装置組み込みも対応

※英語版カタログをダウンロードいただけます。

※詳しくはPDF資料をご覧いただくか、お気軽にお問い合わせ下さい。

3.5インチ、8スロットのHDDトレー取り出し可能な仕様です。

『HT-2』は、組成がAl-2%Fe-1%Cuからなるダイカスト用高熱伝導合金です。

Feは焼付き防止効果があり、Cuは強度を上げる効果を発揮。

高熱伝導率を得るため、不純物成分は低含有量となっています。

【特長】

■組成はAl-2%Fe-1%Cu

・Fe:焼付き防止効果

・Cu:強度を上げる効果

■熱処理なしで高熱伝導率が得られる

■試験片が金型に焼付かない

■割れも発生せず、薄肉の金型にも充填される

※詳しくはPDFをダウンロードして頂くか、お気軽にお問い合わせ下さい。

お探しの製品は見つかりませんでした。

1 / 1

回路・パターン設計における設計データの検証時間短縮

回路・パターン設計における設計データの検証時間短縮とは?

半導体設計において、回路図やレイアウトといった設計データの正確性を保証するための検証プロセスは不可欠です。しかし、設計の複雑化に伴い、この検証に要する時間が長期化する傾向にあります。本テーマでは、この検証時間の短縮を目指す取り組みについて解説します。目的は、製品開発サイクルの迅速化、コスト削減、そして市場投入までのリードタイム短縮を実現することです。

課題

検証工数の増大

回路規模や機能の複雑化により、網羅的な検証に必要な工数が指数関数的に増加し、検証期間が長期化しています。

設計変更への追従遅延

設計途中で発生する仕様変更や不具合修正に対し、検証プロセスが追従できず、手戻りや遅延が発生しやすくなっています。

検証環境の構築・維持コスト

高度な検証ツールや大規模な計算リソースが必要となり、その導入・運用・保守に多大なコストがかかっています。

専門人材の不足

高度な検証技術を持つ専門人材の確保が困難であり、限られたリソースで多くの検証タスクをこなす必要があります。

対策

自動化ツールの活用

検証プロセスの一部または全体を自動化するツールを導入し、手作業による時間を削減し、ヒューマンエラーを低減します。

早期検証・段階的検証

設計の初期段階から検証を開始し、段階的に検証範囲を広げることで、早期に問題を特定し、手戻りを最小限に抑えます。

検証手法の最適化

シミュレーション、フォーマル検証、ハードウェアエミュレーションなど、目的に応じた最適な検証手法を選択・組み合わせます。

クラウドベースの検証プラットフォーム

オンデマンドでスケーラブルな計算リソースを利用できるクラウドプラットフォームを活用し、検証環境の構築・維持コストを削減します。

対策に役立つ製品例

統合検証システム

回路シミュレーション、レイアウト検証、フォーマル検証などを統合し、一元管理することで、検証ワークフロー全体の効率化と時間短縮を実現します。

AI駆動型検証支援ツール

過去の検証データや設計パ�ターンを学習したAIが、潜在的な不具合箇所を予測・提示することで、検証の網羅性を高めつつ、時間を効率化します。

分散コンピューティング検証サービス

大規模な検証タスクを複数の計算ノードに分散処理させることで、検証時間を劇的に短縮し、複雑な設計データにも対応可能にします。

設計データ管理・自動チェックシステム

設計データの変更履歴管理と、定義さ��れたルールに基づいた自動チェックを組み合わせることで、検証漏れを防ぎ、迅速なフィードバックを実現します。

⭐今週のピックアップ

読み込み中